就在刚刚,基本半导体在其微信公众号发布了铜烧结方案进展。

信息显示,基本半导体目前已经对多款铜烧结浆料进行了选型评估,印刷、烘烤、贴片、烧结等工艺环节已趋于稳定。主要从三个方面来考量其可行性。

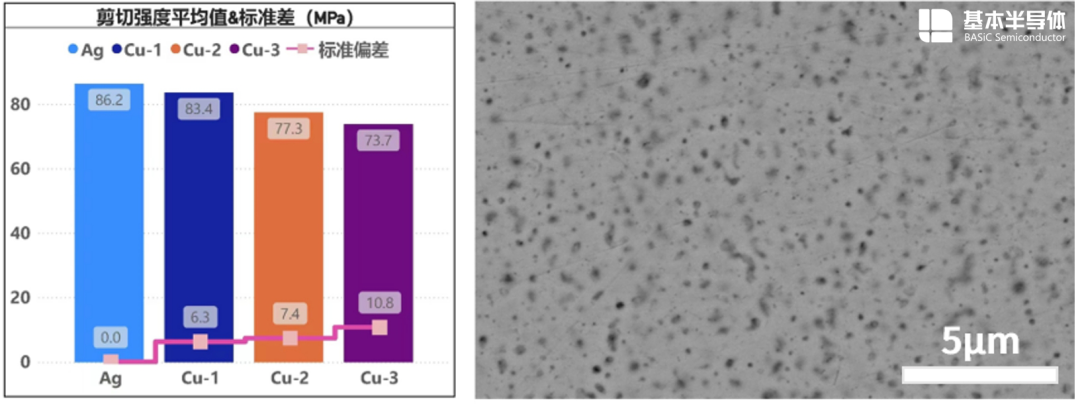

一是烧结后的连接强度达到80Mpa以上,接近银烧结浆料的最优水平。

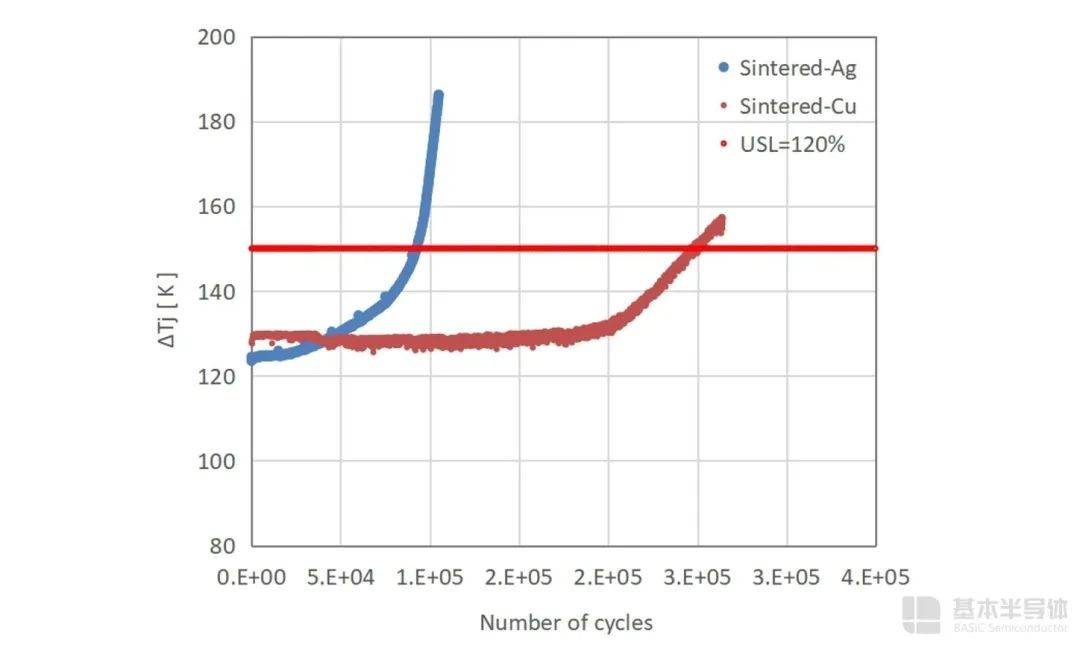

二是在热冲击测试中,铜烧结展现了高可靠性。寿命表现超过了银烧结模块30%,并且没有观察到明显的界面破坏。

三是在功率循环可靠性测试中,采用铜浆料的模块样品寿命远高于银浆料的模块。

通过对样品功率模块测试表明,采用铜烧结技术的预研产品展现出了优异的性能和可靠性。因此基本半导体认为铜烧结技术在碳化硅车载功率模块封装领域大有可为。

01、铜烧结和银烧结目的是相同的

在汽车驱动系统中,以碳化硅为代表的第三代半导体凭借良好的开关损耗、耐温性能,未来将替代一部分IGBT成为主驱功率器件的首选。

由于工作的温度的提升,传统的锡焊就没有办法满足温度的要求。因此就需要开发新的焊接方式。新的焊接需要满足耐高温的同时,还需要具备一定的高导热性能。

烧结铜和烧结银就在这个背景下开始被研发和应用 。

铜和银的熔点温度约在1000度左右,铜略高于银。虽然耐温性能可以满足,但由于其熔点温度实在太高,在实际工艺中超过了半导体材料的温度最大限制。所以就需要开发一种熔点较低且耐温性能不变的材料。

纳米技术的发展使之成为可能。纳米材料随着尺寸的减小,其烧结温度也会随之降低,远低于其熔点,即为纳米材料的尺度效应。采用纳米技术后,纳米银和纳米铜的烧结温度约在200度左右,大幅低于其自身材料熔点,使得在封装技术中应用成为可能。

02、银烧结量产较快,铜烧结也没有完全掉队

在实际应用中,银烧结工艺应用速度快于铜烧结。目前几乎碳化硅功率模块采用的都是银烧结技术。并且应用的位置也较多。 一是在芯片和基板或者铜夹的连接处,该处连接是最普遍的一个位置。二是用在模块与散热器的连接处,比如博世PM6以及特斯拉的TPAK。

并且银烧结的整个产业链也比较成熟,除了外资企业外, 国内的企业比如硅酷可以做热压设备,深圳先进和快克可以做烧结设备,并且已经能够应用量产。相对来说设备的选择也更多。

之所以银烧结应用较快, 一个很重要的原因是银在空气中比较稳定,不易氧化。在工艺方面更易于实现。另外,纳米铜的制备也要难于纳米银。

虽然银烧结发展速度明显比铜烧结快, 但铜烧结也有银烧结无法达到的优势。

首要并且是关键的优势, 铜烧结理论价格要远低于银烧结。其核心在于纳米铜要比纳米银便宜。 一个功率模块大约需要15克左右纳米银,早期的纳米银一克到过400元,价格非常昂贵。现在随着大规模应用,一克纳米银的价格大概在30元左右,如此测算的一个模块银烧结的成本在400-500元之间。所以这除了芯片本身外,碳化硅功率模块价格较高的主要原因之一。 这也是为什么目前有考虑在碳化硅功率模块中重新尝试部分再次使用锡焊的原因。铜烧结因为目前尚未有大规模量产的案例,所以只有理论价格测算。 按照基本半导体测算,烧结铜的价格是烧结银的几十分之一(有可能是通过金属铜和金属银的对比)。

其次是 关于性能方面。一是 铜烧结的熔点更高,因此理论材料疲劳性能要优于银烧结。基本半导体热冲击试验也说明了这一点。二是 基板表面同样是铜,两者材料相同,所以界面更加稳定稳定。基本半导体也提到, 单纯的界面组成也能够最大限度地抑制原子扩散、金属间化合物生成等互连退化现象,降低界面处的接触电阻、热阻,并优化电流分布。

正是因为这两个关键优势,使得业内对铜烧结的工艺从未停止。这其中就包括材料厂商, 贺利氏就宣布其运用独特的造粉技术和溶剂体系,开发出由微米铜构成的烧结铜浆料 。并强调浆料适合长达八小时的连续印刷时间,烧结后的质量不会受到氧化的影响,同时,烧结强度也能达到与烧结银相近的水平。对于工艺中存在的易氧化问题,贺利氏推荐使用"湿贴"工艺,主要有两个优点。一是先贴芯片后烘干的工艺可以规避微米铜颗粒在空气环境下的热贴芯片引入的铜氧化风险,同时也可以提供更好的初步贴片强度。二是在铜浆仍然具有流动性的状态下贴片可以消除一系列因印刷不良引入的缺陷。

虽然业内诸多企业在尝试铜烧结技术,但基于目前的情况很难判断未来是否能对银烧结形成一定的替代,因为毕竟纳米银的价格也在处于下降通道中,并且比铜烧结更加成熟。但新技术的尝试在一定程度也会促进两者技术的进一步发展,最终则是加速碳化硅功率模块的应用。

沪公网安备31010702008139

沪公网安备31010702008139